UDK 519.713

# Synchronizing and Homing Experiments for Input/output Automata

Kushik N.G. (SAMOVAR, CNRS, Télécom SudParis / Université Paris-Saclay),

Yevtushenko N.V. (Tomsk State University, Institute for System Programming of the

Russian Academy of Sciences)

Burdonov I.B. (Institute for System Programming of the Russian Academy of Sciences)

Kossatchev A.S. (Institute for System Programming of the Russian Academy of Sciences)

The paper is devoted to studying the ('gedanken') experiments with input/output automata. We propose how to derive proper input sequences for identifying the final (current) state of the machine under experiment, namely synchronizing and homing sequences. The machine is non-initialized and its alphabet of actions is divided into disjoint sets of inputs and outputs. In this paper, we consider a specific class of such machines for which at each state the transitions only under inputs or under outputs are defined, and the machine transition diagram does not contain cycles labeled by outputs, i.e. the language of the machine does not contain traces with infinite postfix of outputs. Moreover, for each state where the transitions under inputs are defined, the machine has a loop under a special quiescence output. For such class of input/output automata, we define the preset synchronizing and homing experiments, establish necessary and sufficient conditions for their existence and propose techniques for their derivation. The procedures for deriving the corresponding ('gedanken') experiments for input/output automata are based on the well-studied solutions to these problems for Finite State Machines.

Keywords: Input/Output Automata, Synchronizing Sequence, Homing Sequence

#### 1. Introduction

The state identification problem using 'gedanken' experiments with Finite State Machines (FSMs) is a long standing problem. The first results were obtained by Moore [10] and have been then improved by many researchers [3, 6, 9]. A ('gedanken') state identification experiment with an FSM consists of applying an input sequence to a machine under investigation, observing the output response and drawing a conclusion about initial or current state. If the conclusion is drawn about the

initial state (a state before the experiment) then the experiment is called *distinguishing*. When the conclusion is drawn about the current FSM state (a state after the experiment) then the experiment is called *homing* or *synchronizing*. Depending on the way how an input sequence is applied an experiment can be *preset* or *adaptive*. In this paper, we discuss only preset experiments when an applied input sequence is derived in advance.

There are many applications of such 'gedanken' experiments and a big body of work is developed for constructing preset and adaptive experiments [4, 7, 11]. Most applications are related to decreasing the complexity of deriving a test suite with the guaranteed fault coverage when the specification FSM has homing/synchronizing/distinguishing sequences and there are many papers how such sequences can be derived for deterministic and nondeterministic, complete and partial FSMs [2, 5, 7, 11]. In [8], the authors propose how homing and synchronizing sequences can accelerate/optimize the monitoring of communicating systems. When the initial/current state of an Implementation Under Test (IUT) is known, the set of properties that should be verified at a given IUT state can be dramatically reduced.

However, FSMs have limited capacity when describing software component behavior. The reason is that the next input can be applied only when the FSM under investigation produced an output to the previous input. On one hand, this allows to escape races between inputs and outputs and it is one of the reasons why test suites with the guaranteed test coverage are derived mostly against FSMs. On the other hand, FSM notion does not allow to consider the situations when an output can be produced only after a sequence of inputs has been applied to an IUT and moreover, not a single output can be produced but a sequence of outputs. Such situations can be described when using Input/Output automaton as a model; an Input/Output automaton has the finite number of states but differently from FSMs, transitions between states are labeled not by a pair <input, output> but by a single input or output. To the best of our knowledge there are no investigations on homing/synchronizing sequences for such model.

In this paper, we study the state identification problem for Input/Output automata when at each state, only inputs or only outputs are allowed. We define the notions of homing/synchronizing sequences for such Input/Output automata and adapt the known techniques for deriving such sequences for a new model. Therefore, the main contribution of this paper is the definition of homing/synchronizing sequences for Input/Output automata and the development of techniques for the existence check and derivation.

The rest of the paper is structured as follows. Section 2 contains preliminaries. Techniques for deriving homing and synchronizing sequences for input/output automata are proposed in Section 3. Section 4 concludes the paper and has a brief discussion on the directions of the future work.

We note that this work is partially supported by the Russian Science Foundation (RSF), project  $N_2$  16-49-03012.

#### 2. Preliminaries

An Input/Output *Automaton* (or an *automaton* in this paper) is a 4-tuple  $S = (S, I, O, T_S)$  where S is a finite set of states; I and O are finite non-empty disjoint sets of inputs and outputs, respectively;  $T_S \subseteq S \times I \times S \cup S \times O \times S$  is a *transition relation* where 3-tuples  $(s, i, s') \in T_S$  and  $(s, o, s') \in T_S$  are *transitions*.

In this paper, we consider a specific class of automata for which the following holds:

- i) At each state only inputs or only outputs are allowed, i.e.  $S = S_1 \cup S_2$ ,  $S_1 \cap S_2 = \emptyset$  and  $T_S \subseteq S_1 \times I \times S \cup S_2 \times O \times S$ ;

- ii) The transition diagram does not contain cycles/loops labeled with outputs, i.e. the language of the machine does not contain traces with infinite postfix of outputs;

- iii) The machine has a special output  $\delta \notin O$  that represents the quiescence [12] at the states where the transitions under inputs are defined; at each state  $s \in S_1$ , there is a loop under  $\delta$ , namely  $(s, \delta, s) \in T_S$ .

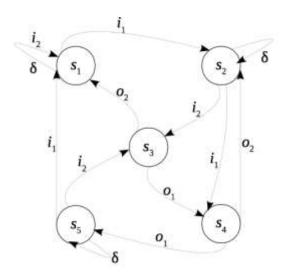

As an example of an Input/Output automaton, consider a machine in Fig. 1. The automaton S has five states, namely  $S = \{s_1, ..., s_5\}$ , where  $S_1 = \{s_1, s_2, s_5\}$  and  $S_2 = \{s_3, s_4\}$ . At each state from the set  $S_1$  the automaton accepts inputs  $i_1$  and  $i_2$ . However, when the machine is at state  $s_3$  or  $s_4$  no inputs can be accepted and only outputs  $o_1$  or  $o_2$  can be produced.

Fig. 1 – An input/output automaton S

As usual, synchronizing and homing experiments are used to identify the final (current) state of the machine under experiment, i.e., the state reached by the machine after an appropriate input sequence has been applied when the initial state of the machine was unknown. In this paper, we adapt the notion of a 'gedanken' experiment in the way that it can be used for the input/output automata for which corresponding synchronizing and homing sequences can be defined.

The experiment is performed under the following **hypothesis**:

We assume that before applying any input, a tester (or any experimenting entity) waits for a given maximal output timeout t. The experiment is performed as follows: the tester expects an output in t time units; if the machine produces one, then the timer is reset and the tester waits for another t time units. If no output is produced by the system in t time units then the tester applies the next input (if any) and resets the timer.

The latter explains the necessity of introducing the specific output  $\delta \notin O$ , namely whenever the output is not observed we assume that the system/machine produced the output  $\delta$ . Such extension of the output alphabet allows to define the corresponding synchronizing and homing sequences for an Input/Output automaton.

As usual, a synchronizing sequence is an input trace such that after its application independent of the initial state, the current state of the machine is known. In other words, a sequence  $\alpha = i_1 i_2 ... i_k$  is *synchronizing* for the automaton S if there exists a state  $s \in S$  such that for each trace  $\beta_1 i_1 \beta_2 i_2 ... \beta_k i_k \beta_{k+1}$  where p is the length of a longest sequence of consecutive outputs and  $\beta_j \in (O \cup \{\delta\})^p$ , j = 1, ..., k+1, it holds that the  $\beta_1 i_1 \beta_2 i_2 ... \beta_k i_k \beta_{k+1}$ -successor of the set  $S(\beta_1 i_1 \beta_2 i_2 ... \beta_k i_k \beta_{k+1}$ -state-after-S) is either empty or equals  $\{s\}$ . We note that hereafter the  $\gamma$ -successor of the state  $s \in S$  is the set of states that can be reached from state s through the trace  $\gamma$  while the  $\gamma$ -successor of S has every state that is reached from some state of S through the trace  $\gamma$ .

A homing sequence allows to determine the final (current) state of the machine under experiment via the observation of its output response. Therefore, a sequence  $\alpha = i_1 i_2 ... i_k$  is *homing* for the automaton S if for each trace  $\beta_1 i_1 \beta_2 i_2 ... \beta_k i_k \beta_{k+1}$ ,  $\beta_j \in (O \cup \{\delta\})^p$ , j = 1,..., k+1, it holds that the  $\beta_1 i_1 \beta_2 i_2 ... \beta_k i_k \beta_{k+1}$ -successor of the set S is either empty or is a singleton.

For an automaton **S** in Fig. 1 a homing sequence  $\alpha$  is  $\alpha = i_1 i_1$ .

## 3. Deriving synchronizing and homing sequences for input/output automata

In this section, we discuss how homing and synchronizing sequences defined above can be derived against input/output automata. We also establish necessary and sufficient conditions for the existence of such sequences for the machines of the class/type described above.

#### 3.1. Deriving synchronizing experiments

We propose to derive a synchronizing sequence for an automaton S where actions are divided into inputs and outputs via an iterative elimination of the transitions labeled by outputs. Such transition can always be omitted as for the automata class considered in this paper, there does not exist a state where transitions under inputs and outputs are defined at the same time. In other words, we propose to derive an automaton where only the transitions under inputs are left. Synchronizing sequences for such kind of automata are well studied [2, 5, 11, 13] and thus, classical methods for their derivation can be further applied.

#### **Procedure 1**

**Input**: Input/Output automaton  $S = (S, I, O, T_S)$

**Output**: Synchronizing sequence  $\alpha$  or a message "The automaton S is not synchronizing"

**Step 1.** Derive an automaton  $A = (S_1, I, T_A)$  with the empty set of transitions, i.e.  $T_A = \emptyset$ .

**Step 2.** For each transition  $(s, i, s'') \in T_S$ , where  $s, s'' \in S_1$ , add to  $T_A$  the transition (s, i, s''); for each transition (s, i, s''), where  $s \in S_1$  and  $s'' \in S_2$ , add to  $T_A$  the transition (s, i, s''') where state  $s''' \in S_1$  and s''' is in a  $\beta$ -successor of s'' in the automaton  $S, \beta \in O^*$ .

**Step 3.** Check the existence and derive, if possible, a synchronizing sequence  $\alpha$  for the automaton A:

If the sequence  $\alpha$  is derived then **Return**  $\alpha$ ;

**Else Return** the message "The automaton S is not synchronizing"

**Proposition 1**. The automaton S is synchronizing if and only if the automaton A in Procedure 1 is synchronizing. Moreover, each synchronizing sequence  $\alpha$  for A is a synchronizing sequence for S.

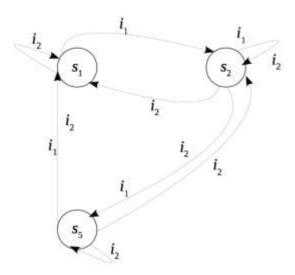

As an example, check the existence of a synchronizing sequence for an automaton in Fig. 1. The corresponding automaton A derived over the inputs of S is presented in Fig. 2.

By direct inspection, one can assure that the automaton A in Fig. 2 is not synchronizing. Therefore, due to Proposition 1, the automaton S does not have a synchronizing sequence.

Fig. 2 – An automaton A derived through the application of Procedure 1

#### 3.2. Deriving homing experiments

Similar to the derivation of synchronizing sequences we propose to reduce the problem of checking the existence and derivation of a homing sequence for an input/output automaton to that one for classical Finite State Machines (FSMs) as there are a number of such techniques for FSMs [see, for example 6-8].

#### **Procedure 2**

**Input**: Input/Output automaton  $S = (S, I, O, T_S)$

**Output**: Homing sequence  $\alpha$  or the message "The automaton S is not homing"

**Step 1.** Derive an FSM  $M = (S_1, I, O \cup O^2 \cup \square ... \cup O^p \cup \square \{\delta\}, T_M)$  with the empty set of transitions, i.e.,  $T_M = \emptyset$ , where p is the length of a longest output trace of the automaton S.

**Step 2.** For each state  $s \in S_1$ , such that  $(s, i, s') \in T_S$ ,  $s' \in S_1$ , add to the  $T_M$  the transition  $(s, i, \delta, s')$ .

**Step 3.** For each state  $s \in S_1$ , such that  $(s, i, s') \in T_S$ ,  $s' \in S_2$ , add to the  $T_M$  the transition  $(s, i, o_1 o_2 \dots o_k, s'')$ ,  $k \le p$ , where  $s'' \in S_1$  is the  $o_1 o_2 \dots o_k$ -successor of state s'.

**Step 4.** Check the existence and derive, if possible, a homing sequence  $\alpha$  for the FSM M:

If the sequence  $\alpha$  is derived then **Return**  $\alpha$ ;

**Else Return** the message "The automaton *S* is not homing"

**Proposition 2.** A sequence  $\alpha$  is homing for the automaton S if and only if  $\alpha$  is a homing sequence for the FSM M.

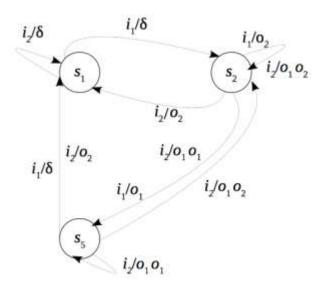

As an example, check the existence of a homing sequence of an automaton S in Fig. 1. This automaton does not have a synchronizing sequence, nevertheless, a homing one can still exist. In order to check the existence of a homing sequence we derive an FSM M of Procedure 2 for the automaton S in Fig. 1. The obtained FSM M is shown in Fig. 3.

Fig. 3 – An FSM *M* derived from *S* using Procedure 2

The application of classical methods [6, 7, 11] for the homing sequence derivation for the FSM M can return a sequence  $\alpha = i_1 i_1$ . Therefore, the sequence  $\alpha = i_1 i_1$  is a homing sequence for the automaton S in Fig. 1.

We note that the computational complexity of the existence check is the same (or at least not better than) as for corresponding automata and FSMs. The reason is that when deriving a synchronizing sequence an automaton that does not have output actions can be considered while for deriving a homing sequence a classical FSM can be represented as an Input/Output automaton by

\_

presenting each FSM transition i/o as a pair of consecutive transitions under i and o. The latter means that for input/output automata that lead to the derivation of synchronizing/homing sequences for (partial) nondeterministic automata/FSMs the length of such sequences is exponential with respect to the number of states of the machine. Therefore, one of interesting issues for the future work is the development of the approaches for decreasing this complexity or to specify classes of Input/Output automata where the complexity can be reduced.

#### 4. Conclusion

In this paper, we have studied the problem of deriving homing/synchronizing sequences for Input/Output automata. We have limited the class of such automata with automata where at each state, only inputs or only outputs are defined. We have shown how for such automata, the known techniques for deriving homing/synchronizing sequences for automata and FSMs can be adapted. To the best of our knowledge there are no papers where homing/synchronizing sequences are derived for Input/Output automata. We also mention that a number of examples of using Input/Output automata for describing the behavior of (components) of discrete event systems can be found in [1, 12].

As for the future work, we are mostly concerned how to extend the obtained results to adaptive sequences including distinguishing sequences as well as how to expand the class of Input/Output automata for such 'gedanken' experiments.

An interesting question is about Input/Output automata with a nonobservable action  $\tau$ . In this case, the nondeterminism degree of the automaton will be increased and more assumptions on the automaton behavior should be made when deriving homing/synchronizing sequences.

Another question is about considering Input/Output automata where both inputs and outputs are specified at some state. It is quite possible that in this case, more assumptions have to be made about the implementation/execution of a 'gedanken' experiment and we are going to try our hand in establishing such minimum assumptions.

As most problems of checking the existence and derivation of synchronizing and homing sequences for partial and non-deterministic automata and FSMs are PSPACE-complete, there is an interesting question about defining Input/Output automata classes where the complexity can be decreased. One possible way to decrease this complexity can be to consider adaptive synchronizing and homing experiments instead of preset, however this issue needs more investigation.

Based on the experience of constructing adaptive state identification experiments for FSMs, we suppose that in this case, we will face the same problems as discussed above and it is our first

priority to define and construct adaptive homing/synchronizing experiments at least for the class of Input/Output automata described in this paper.

The problems listed above, as well as many others, form the directions for the future work.

#### References

- 1. Бурдонов И.Б. Теория конформности для функционального тестирования программных систем на основе формальных моделей: дис. . . . док. физ.-мат. наук. Москва, 2008. 596 с.

- 2. Мартюгин П.В. Нижние оценки длины кратчайших бережно синхронизирующих слов для двухи трёхбуквенных частичных автоматов // Дискретн. анализ и исслед. опер. 2008. №4. Т. 15. С. 44-56.

- 3. Gill A. State-identification experiments in finite automata // Information and Control. 1961. P. 132-154.

- 4. Hierons R. M., Jourdan G.-V., Ural H., Yenigun H. Using adaptive distinguishing sequences in checking sequence constructions // ACM symposium on Applied computing: proceedings. 2008. P. 682-687.

- Ito M., Shikishima-Tsuji K. Some Results on Directable Automata // Theory Is Forever. LNCS. 2004.

№3113. P. 125-133.

- 6. Kohavi Z. Switching and Finite Automata Theory. McGraw-Hill: New York, 1978.

- Kushik N., El-Fakih K., Yevtushenko N., Cavalli A. R. On Adaptive Experiments for Nondeterministic Finite State Machines // Software Tools for Technology Transfer. 2016. 18 (3). P. 251-264.

- 8. Kushik N., López J., Cavalli A.R., Yevtushenko N. Improving Protocol Passive Testing through "Gedanken" Experiments with Finite State Machines // QRS: proceedings. 2016. P. 315-322.

- 9. Lee D., Yannakakis M. Testing finite-state machines: state identification and verification // IEEE Trans. on Computers. 1994. 43(3). P. 306-320.

- 10. Moore E.F. Gedanken-experiments on sequential machines // In Automata Studies (Annals of Mathematical Studies no.1). Princeton University Press. 1956. P. 129-153.

- 11. Sandberg S. Homing and Synchronization Sequences // Model Based Testing of Reactive Systems. LNCS. 2005. №3472. P. 5-33.

- 12. Tretmans J. Test Generation with Inputs, Outputs and Repetitive Quiescence // Software Concepts and Tools. 1996. 17 (3). P. 103-120.

- 13. Volkov M. Synchronizing Automata and the Černý Conjecture // 2nd Int'l. Conf. Language and Automata Theory and Applications: proceedings. 2008. P. 11-27.

UDC 004.451,004.415.5

## Verification of Operating System Components

Alexey V. Khoroshilov (Institute for System Programming of RAS)

Victor V. Kuliamin (Institute for System Programming of RAS)

Alexander K. Petrenko (Institute for System Programming of RAS)

The paper concerns recent advances in reaching the goal of industrial operating system (OS) verification. By industrial OS we mean a system actively used in some industrial domain, elaborated and maintained for a significant time, not a proof-of-concept OS developed with mostly research intentions. We consider decomposition of this goal into tasks related with various functional components of OS and various properties under verification, and application of different verification methods to those tasks. This is a trial to explicate and summarize the experience of several projects on various OS components and different OS features verification conducted in ISP RAS.

Keywords: Operating system, verification, testing, monitoring, static analysis, deductive verification

#### 1. Introduction

Modern industrial operating systems, which are used for plenty of real-life applications, are rather complex. They are not just very large pieces of code, they also have a great number of heterogeneous features, should operate on a large variety of hardware from diverse manufacturers, and are to provide for application developers numerous interfaces, which are expected not only to work correctly, but also to use underlying hardware in effective, efficient, and fault-tolerant way. By industrial operating system (OS) we mean in this article an OS actively used in some industrial domain (or a general purpose one), elaborated and maintained for a significant time. We do not discuss here OSes developed with certain research purposes or as a proof-of-concept, they may be much more simple than industrial ones and have different specifics.

An OS is supposed to perform two main tasks.

- It should organize operation of multiple applications on some machine, managing hardware resources, and protect applications from interfering each other.

- It should provide interface for application developers to use those resources in a convenient way, and also to transfer data between applications, if needed.

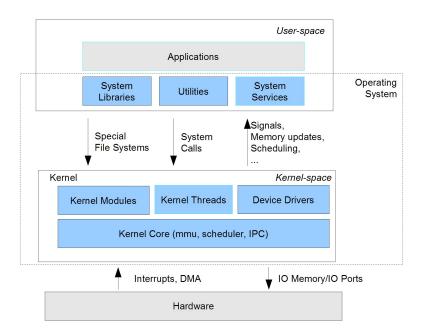

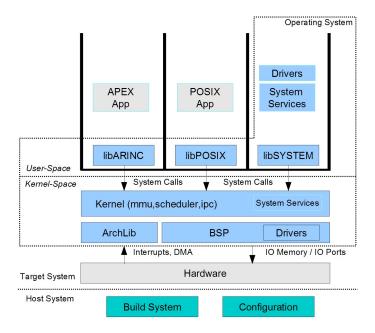

Fig. 1. Main parts of general purpose OS

The main part of an OS is *a kernel*, which works in privileged processor mode (kernel mode) and so has unbounded access to all system resources. Kernel manages application access to hardware resources, sets access policies, and prevents their violation. Some functions that do not require privileged mode are also sometimes included into kernel for efficiency.

Applications can interact with kernel mostly with system calls, which are calls of kernel functions with switch into privileged mode. There are additional ways to interact with kernel, like special file systems (procfs, sysfs, debugfs) in Linux. To provide convenient environment for application developers OS usually provides system libraries and utilities, implementing frequently used functions that require interaction with kernel. To solve tasks that need activity from the kernel side, system services are provided. Such tasks include communication protocols, managing special devices, etc. Corresponding services can work in kernel mode or in user mode. Figures 1 and 2 show the structure of general purpose OS and real-time OS correspondingly.

The above sketchy review of OS structure gives some hints on its complexity. The verification of industrial OS is also rather complex, especially if one takes into consideration the following.

- A plenty of features of modern OS provide various feature interaction cases and corner cases, where much more scrutinized inspection of required behavior is necessary.

- Multitasking support in modern OS makes checking behavior correctness much more intricate.

- Basic OS functionality must be available in spite of some faults in hardware or software

Fig. 2. Main parts of real time OS

components. This fault tolerance should also be verified.

- Modern OS usually supports network communications and provides a workplace for many

users. It ensures certain security policies, setting restrictions on data and operations

available for different users and processes. Those restrictions should be preserved in case

of faults and attacks from malicious users or software components coming from network.

- Support of huge variety of heterogeneous hardware is usually implemented as deep configurability of an OS. So, one needs verification of OS behavior in various possible configurations, the total number of which is usually larger than astronomical numbers.

- The mere code size and number of functions in modern OS are great. The size of Linux kernel version 4.1 is reported [1] to be about 20.3 million lines of code (LOC), while drivers part, which is created and supported by diverse developers and is responsible for most of bugs is about 11.5 million LOC. The size of Windows XP is estimated as 45 million LOC [2]. The number of functions in system libraries of Debian 7.0 is about 720 thousand [3], while the number of system calls is about 350.

The numbers provided make the goal of thorough verification of industrial OS unreachable at this moment. Nevertheless, the developer community needs some methods to assure correctness, efficiency, security, and fault tolerance of modern OSes. The only reasonable way to help is to use various available verification methods to ensure those properties for some parts of OS code or functionality, or to ensure only a few critical properties on OS as a total. Important

results of partial verification are faults and errors found, so, although we cannot now guarantee strict correctness or security of an OS, we can come closer to them (if we do not forget about that ultimate goal in routine quality assurance processes). Thus, increasing scalability of used methods and tools step by step, we can enlarge the verified parts of code and functionality, targeting to reach the goal of complete verification somewhen in future.

In this paper we review the activity on verification of different parts and features of OSes performed in the Institute for System Programming of Russian Academy of Sciences in a dozen of projects conducted last 20 years. This activity uses and integrates different methods of verification for different OS properties and components, applying them to Linux OS and several specialized real-time OSes. The main methods used are as follows.

- Testing and dynamic analysis. Testing can be performed in different ways. The most lightweight testing focuses on producing test cases for basic behavior of functions, skipping consideration of complex or even non-so-often cases. The main target test completeness criterion for such testing is coverage of functions. The most thorough testing is intended to provide as strict and accurate checks as possible. It uses formal specification of required behavior, tries to formulate presumptions and strict guarantees concerning the correctness of tested system, and is targeted on coverage of all conditions met both in code and requirements, along with some corner cases (buffers overflow, failures of underlying hardware, processing simultaneous events, etc.). Various testing methods between these two extremes are also used. The main properties under test are functional, but testing is also the main method to check efficiency and fault tolerance. Along with testing other dynamic analysis methods, not requiring preparation of test suites, can be used.

- Static analysis. Static analysis also presents a wide range of approaches, from simple, quick, and lightweight checkers seeking a bounded number of bug patterns and producing a lot of false positives reports on bugs, which actually aren't, to rather complex tools using formal specifications and configurable analyses, capable to catch very intricate bugs, requiring large effort during their configuration, usually with not-so-high numbers of false positives. Static analysis is widely used to check various code, but usually more complex and powerful techniques are applied to components with more strict requirements, like OS kernel modules.

- **Deductive verification.** Deductive verification is used to verify most important security or correctness properties. There are well-known examples of OS kernel verification [4–6],

but in all cases the verified code is much smaller than kernels of typical industrial OS. Nevertheless, deductive verification techniques can be applied to industrial OS code and provide valuable results.

Below we explicate and try to summarize the experience obtained by ISP RAS in dozens of projects, where some kind of verification was performed on various components of industrial OSes (Linux and several real-time OSes for specific domains). The paper organized as follows. In Section 2 we provide review of testing techniques used to check different OS components. Section 3 reports on application of various static analysis techniques, usually in conjunction with some dynamic analysis. Section 4 describes our results in deductive verification of OS security. Then the Conclusion sums up the exposition and describes possible further development.

#### 2. Testing and dynamic analysis

ISP RAS develops OS components testing methods since its foundation in 1994. The first such results are related with KVEST [7], a method for test generation based on formal specifications of functional behavior in form of software contracts, used to construct several test suites for real-time OS developed and maintained by Nortel Networks.

## 2.1. Formal approaches

Later this approach was refined and extended into UniTESK method [8]. The basic ideas of the method are as follows.

- Requirements to library functions behavior are specified as *software contracts* preconditions, postconditions, and data type invariants (they may be considered as common parts of pre- and postconditions of all functions dealing with those data types). Software contracts are written in extension of C language or with the help of specialized libraries in pure C/C++.

- Test completeness criteria are formulated as coverage of branches in postconditions. If there is a need to add some situations to coverage goals, they are formulated as specific additional branches, not related with behavior restrictions.

- Test scenarios are represented as extended finite state machines, for which execution of all reachable transitions guarantees coverage of all coverage goals (branches) specified in postconditions of functions called (each transition corresponds to a sequence of function calls). The control state of test scenario is a generalization of data structures used in

specifications of functions tested by this scenario.

- Testing is performed by automatic traversal of a state machine defined in test scenario.

Each call to a function under test is augmented with call to the oracle function generated from postcondition and evaluating correctness of the results obtained.

- Testing of parallelism is based on interleaving semantics [9]. It is performed by gathering all the observed events (function calls, function returns, and others) and constructing a linear sequence of those events, in which all pre- and postconditions hold. If such a sequence cannot be constructed, a bug is recorded.

UniTESK was used for conformance test suite creation for Core part of Linux Standard Base (LSB), which describes system libraries and almost coincides with POSIX, in OLVER Project [10], where 1532 functions of LSB Core was formally specified and tested. The same method was applied in conformance test suite development for ARINC-653 part 1 standard [11] describing 54 functions.

Another test construction method, not using formal specifications, but based on formal investigation of requirements was used to create conformance tests for mathematical functions working with floating-point numbers in POSIX system libraries [12]. The method uses as test data specific floating point values, including numbers having patterns in mantissa (like 0000FFFFAAAA in hexadecimals), boundaries of domains of specific function behavior (such behaviors include monotonicity, sign preservation, well-known asymptotics), and so-called worst cases, numbers, for which correct function calculations requires much more precision than in average. For now test suites for 104 functions was developed.

## 2.2. Informal approaches

Several other methods used for test construction in ISP RAS are not based on formal specifications, but targeted on strict requirements traceability, so that tests are developed to check certain explicitly formulated requirements and they report on violation of this requirements (providing their ids) when find some bug.

The first method [13] is based on manual test case development with further parameterization making a test case a template. For test execution each template is supplemented with several arrays of arguments that are put in place of corresponding parameters. The method was used to create tests for more than 4000 functions in Linux system libraries, they detected about 40 bugs.

Another approach [14] provides automatic generation of sanity tests (checking only basic functionality) on the base of initialization procedures for data type values and libraries and preconditions of functions specified manually and stored in a database. This method provides rather surface testing, but can be used for massive test generation with little effort. It was applied to Linux libraries containing about 20000 functions.

#### 2.3. Fault tolerance testing and dynamic analysis

For monitoring Linux kernel modules KEDR framework [15] was developed in ISP RAS. It makes possible to intercept calls from single kernel module, and so to observe its behavior in dynamics. On the base of KEDR the following verification techniques are implemented.

- KEDR Leak Check used to detect memory leaks in kernel modules. It is more convenient for leak detection then kmemleak [16] included in Linux distribution, but cannot be used to check kernel core code.

- Kernel Strider [17] used to detect data races, situations when several threads read and write one region of memory in unordered manner. Kernel Strider gathers information on module execution, which is then analyzed by ThreadSanitizer [18], data race detection tool developed by Google.

- KEDR Fault Simulation [19] used for fault tolerance testing. The testing organized in a following way. First, the module under test is executed in ordinary way and KEDR detects all calls to functions (system calls or calls of hardware-specific operations) that can fail, but very rare do this during real work. Second, for each call the test is executed, in which this call is simulated as failed. This approach helped to detect several bugs in mature file system drivers like ext4.

A specific example of monitoring used to detect data races is given by RaceHound tool [20], which implements the same idea as DataCollider [21]. It detects memory regions where a thread can write, sets hardware breakpoint on access to such regions, and inserts additional wait intervals around memory access operations in other threads in runtime. If this leads to an access to the tapped memory from another thread, a data race is reported.

## 3. Static analysis

To get more efficiency a large part of general purpose OS code is working in kernel mode, where it has many possibilities to damage important OS data structures. Since the code of Linux drivers, which also works in kernel mode, is usually written by developers having good knowledge of hardware and not-so-good in rules of correct operation within Linux kernel, this naturally leads to the situation where more than a half of bugs detected in kernel is related with drivers code [22]. The similar relation is true for Windows OS [23].

To make development of kernel modules less error-prone, one needs specific tools that can check the rules of correct kernel application program interface (API) usage. Microsoft Research offers Static Driver Verifier tool [24] (called SLAM earlier) capable to solve this task for Windows. The similar solution is suggested by ISP RAS for Linux under the name of Linux Driver Verification (LDV) framework [25, 26]. The method used by LDV is the following.

- The rules of correct kernel API usage are specified as software contracts in specific notation extending C language. They are interpreted as aspect advices that should be inserted at the points where the specified API functions are called in the module under check. Being inserted in the module code, advice code creates error, if the rules specified are violated.

- The usage model is created for the module functions. This is important for driver modules, since their functions are not called explicitly. The usage model defines all possible sequences of function calls.

- The code of the module under check is processed by aspect weaver, which inserts rule checking code, and augmented by the usage model.

- The main check is performed by static verifier tool (most often BLAST [27] and CPAChecker [28] are used). The tool analyzes the code trying to solve reachability task whether the error creation instruction can be reached in some execution. If it is reachable, then the corresponding execution scenario demonstrates a bug, incorrect use of kernel API, else the code uses the API functions correctly. Reachability task is solved with the help of counterexample guided abstraction refinement technique (CEGAR) [29], which constructs automatically more and more precise models of code execution, until the error-reaching path in model can be re-executed in real code, or becomes unreachable in the refined model.

LDV detects 5-8 bugs in almost each release of Linux kernel, for now the total number of found bugs is about 2500. It is used routinely to check about 4000 kernel modules.

Another example of static analysis usage is provided by a tool CPALocator [30] developed on the base of CPAChecker and used to search race conditions in OS code.

#### 4. Deductive verification

Deductive verification is usually considered as the most strict and accurate verification technique, at the same time it requires a lot of effort and highly qualified staff to perform it in a productive way. A good review of deductive verification use for OS code is provided by [31].

In ISP RAS projects deductive verification was used to verify security properties of a Linux-based OS modified for specific use in government agencies [32, 33]. The OS is intended to implement a complex security model (called MROSL DP) integrating mechanisms of lattice-based mandatory access control, mandatory integrity control, and role-based access control. All the security mechanisms are implemented with the help of Linux Security Module (LSM) [34], which provides interceptor functions for all access operations in Linux.

First, MROSL DP model was formalized in Event-B and its main security properties (that no subject with less access level can get access to an object with higher confidentiality level; no subject can get access to an object, for which the subject has no a role having right to access to, etc.) were proved. Second, main LSM functions were also formally specified in so-called detailed model, for which the corresponding security properties were also proved. On the third step the contracts of LSM functions should be translated in ACSL, an extension of C language used in code verification framework Frama C/Jessie [35], and this framework should verify the behavior of C code on conformance with the contracts.

Althoug the project is not finished yet, a number of faults was found in the security model itself due to formalization, and several bugs were detected in code during its partial verification.

#### 5. Conclusion

In this paper we provide a systemized review of verification activities used to check various components and features of industrial OS in ISP RAS projects. Although the ultimate goal — the thorough verification of an OS widely used in real-life — still remains unreachable, our experience shows that important advances in that direction were made by research and development community in last years.

The methods and tools developed for different purposes and using different basic approaches — testing, monitoring, static analysis, deductive verification — can enrich each other by borrowing specific modeling or reasoning technique, as it can be shown on example of memory modeling in static analysis and deductive verification tools [36].

One also can see during a last decade an impressive progress in verification techniques

applicable to real software. In the domain of OS verification such progress can be illustrated by a method for deductive verification of multithreaded C programs working with shared data proposed in ISP RAS [37]. We hope that in one-two years it will be implemented and we can see results of its experimental evaluation.

Another direction of future research concerns possibilities to reuse verification artefacts created by some methods in other ones [38].

#### References

- Why is the Linux kernel 15+ million lines of code? https://unix.stackexchange.com/questions/223746/why-is-the-linux-kernel-15-million-lines-of-code/223770. Aug 2015.

- How Many Lines of Code in Windows XP? https://www.facebook.com/windows/posts/155741344475532. Jan 2011.

- 3. Gerlits E.A., Kuliamin V.V., Maksimov A.V., Petrenko A.K., Khoroshilov A.V., Tsyvarev A.V. Testing of Operating Systems // Trudy ISP RAN/Proc. ISP RAS, 2014, 26(1):73-108 (in Russian).

- 4. Bevier W.R. Kit: a Study in Operating System Verification // IEEE Transactions on Software Engineering, 15(11):1382-1396, Nov 1989.

- 5. Alkassar E., Paul W.J., Starostin A., Tsyban A. Pervasive Verification of an OS Microkernel // In: Leavens G.T., O'Hearn P., Rajamani S.K. (eds) Verified Software: Theories, Tools, Experiments. VSTTE 2010. Springer, LNCS 6217:71-85.

- Klein G., Andronick J., Elphinstone K., Murray T., Sewell T., Kolanski R., Heiser G. Comprehensive Formal Verification of an OS Microkernel // ACM Transactions on Computer Systems, ACM, 2014. 32(1), art. 2.

- Burdonov I., Kossatchev A., Petrenko A., Galter D. KVEST: Automated Generation of Test Suites from Formal Specifications // In: Wing J.M., Woodcock J., Davies J. (eds) FM'99 – Formal Methods. FM 1999. Springer, LNCS 1708:608-621.

- 8. Bourdonov I.B., Kossatchev A.S., Kuliamin V.V., Petrenko A.K. UniTesK Test Suite Architecture // In: Eriksson L.H., Lindsay P.A. (eds) FME 2002:Formal Methods Getting IT Right. FME 2002. Springer, LNCS, 2391:77-88.

- Kuliamin V.V., Petrenko A.K., Pakoulin N.V., Kossatchev A.S., Bourdonov I.B. Integration of Functional and Timed Testing of Real-Time and Concurrent Systems // In: Broy M., Zamulin A.V. (eds) Perspectives of System Informatics. PSI 2003. Springer, LNCS 2890:450-461.

- 10. Grinevich A., Khoroshilov A., Kuliamin V., Markovtsev D., Petrenko A., Rubanov V. Formal Methods in Industrial Software Standards Enforcement // In: Virbitskaite I., Voronkov A. (eds) Perspectives of Systems Informatics. PSI 2006. Springer, LNCS 4378:456-466.

- 11. Maksimov A. Requirements-based conformance testing of ARINC 653 real-time operating systems // Proc. of Data Systems In Aerospace (DASIA 2010), ESA SP-682.

- 12. Kuliamin V. Standardization and Testing of Mathematical Functions. // Proc. of Perspectives of System Informatics, PSI 2009. Springer, LNCS 5947:257-268.

- 13. Khoroshilov A., Rubanov V., Shatokhin E. Automated Formal Testing of C API Using T2C Framework // Proc. of International Symposium Leveraging Applications of Formal Methods, Verification and Validation (ISoLA 2008), pp.56-70.

- 14. Zybin R.S., Kuliamin V.V., Ponomarenko A.V., Rubanov V.V., Chernov E.S. Automation of broad sanity test generation // Programming and Computer Software, 34(6):351-363, 2008.

- 15. Shatokhin E. Using Dynamic Analysis To Hunt Down Problems in Kernel Modules // Presentation at LinuxCon Europe 2011, Czech Republic, Prague, 26-28 October 2011.

- 16. kmemleak description. https://www.kernel.org/doc/Documentation/kmemleak.txt.

- 17. Kernel Strider. https://code.google.com/p/kernel-strider/.

- 18. Serebryany K., Iskhodzhanov T. ThreadSanitizer: data race detection in practice // In Proc. of Workshop on Binary Instrumentation and Applications (WBIA 2009). ACM, 2009, pp.62-71.

- 19. Tsyvaerv A., Khoroshilov A. Using Fault Injection for Testing Linux Kernel Components // Trudy ISP RAN/Proc. ISP RAS, 2015, 27(5):157-174 (in Russian).

- 20. Race Hound tool. http://forge.ispras.ru/projects/race-hound.

- 21. Erickson J., Musuvathi M., Burckhardt S., Olynyk K. Effective data-race detection for the kernel // Proc. of USENIX conference on Operating systems design and implementation, OSDI 2010, pp. 151-162.

- 22. Mutilin V.S., Novikov E.M., Khoroshilov A.V. Analysis of typical faults in Linux operating system drivers // Trudy ISP RAN/Proc. ISP RAS, 2012, 22:349-374 (in Russian).

- 23. Ball T., Levin V., Rajamani S.K. A decade of software model checking with SLAM // Communications of the ACM, vol. 54, issue 7, pp. 68-76, 2011.

- 24. Ball T., Bounimova E., Cook B., Levin V., Lichtenberg J., McGarvey C., Ondrusek B., Rajamani S.K., Ustuner A. Thorough static analysis of device drivers // Proc. of ACM SIGOPS/EuroSys European Conference on Computer Systems (EuroSys), pp. 73-85, 2006.

- 25. Mutilin V.S., Novikov E.M., Strakh A.V., Khoroshilov A.V., Shved P.E. Architectire of Linux Driver Verification // Trudy ISP RAN/Proc. ISP RAS, 2011, 20:163-187 (in Russian).

- 26. Zakharov I.S., Mandrykin M.U., Mutilin V.S., Novikov E.M., Petrenko A.K., Khoroshilov A.V. Configurable Toolset for Static Verification of Operating Systems Kernel Modules // Trudy ISP RAN/Proc. ISP RAS, 2014, 26(2):5-42 (in Russian).

- 27. Beyer D., Henzinger T., Jhala R., Majumdar R. The software model checker BLAST: Applications to software engineering // International Journal on Software Tools for Technology Transfer (STTT), vol. 5, pp. 505-525, 2007.

- 28. Beyer D., Keremoglu M.E. CPAchecker: A tool for configurable software verification // Proc. of International Conference on Computer Aided Verification (CAV 2011), Springer, LNCS 6806:184–190.

- 29. Clarke E., Grumberg O, Jha S., Lu Y., Veith H. Counterexample-Guided Abstraction Refinement // In: Emerson E.A., Sistla A.P. (eds) Computer Aided Verification. CAV 2000. Springer, LNCS 1855:154-169.

- 30. Andrianov P.S., Mutilin V.S., Khoroshilov A.V. Adjustable method with predicate abstraction for detection of race conditions in operating systems // Trudy ISP RAN/Proc. ISP RAS, 2016, 28(6):65-86 (in Russian).

- 31. Klein G. Operating system verification An overview // Sadhana, 2009, 34(1):27-69.

- 32. Devyanin P.N., Khoroshilov A.V., Kuliamin V.V., Petrenko A.K., Shchepetkov I.V. Formal Verification of OS Security Model with Alloy and Event-B // Proc. of Int. Conf. on Abstract State Machines, Alloy, B, TLA, VDM, and Z (ABZ 2014), pp. 309–313.

- 33. Devyanin P.N., Khoroshilov A.V., Kuliamin V.V., Petrenko A.K., Shchepetkov I.V. Comparison of specification decomposition methods in Event-B // Programming and Computer Software, 2016, 42(4):198-205.

- 34. Wright C., Cowan C., Morris J., Smalley S., Kroah-Hartman G. Linux Security Module Framework // In: Ottawa Linux Symposium, vol. 8032, 2002.

- 35. Marhé C., Moy Y. The Jessie Plugin for Deductive Verification in Frama-C // INRIA Saclay Île-de-France and LRI, CNRS UMR, 2012.

- 36. Mandrykin M.U., Mutilin V.S. Survey of memory modeling methods in static verification tools // Trudy ISP RAN/Proc. ISP RAS, 2017, 29(1):195-230 (in Russian).

- 37. Mandrykin M.U., Khoroshilov A.V. Towards deductive verification of C programs with shared data // Programming and Computer Software, 2016, 42(5):324-332.

- 38. Petrenko A.K., Kuliamin V.V., Khoroshilov A.V. Integration Points of Operating System Verification Techniques // Trudy ISP RAN/Proc. ISP RAS, 2015, 27(5):175-190 (in Russian).

УДК 004.94, 004.724.4

## **Security of Grid Structures with**

## **Cut-through Switching Nodes**

Shmeleva T.R.

(A.S. Popov Odessa National Academy of Telecommunications)

Store-and-forward buffering of packets is traditionally used in modern network devices such as switches and routers. But sometimes it is a significant obstacle to the quality of service improvement because the minimal packet delivery time is limited by the multiplier of the number of intermediate nodes by the packet transmission time in the channel. The cut-through transmission of packets removes this limitation, because it uses only the head of packet, which contains the destination address, for the forwarding decision. Thus, the cut-through technology of packets transmission has considerable opportunities for the quality of service improving. Models for the computing grid with the cut-through forwarding have been developed in the form of colored Petri nets. The model is composed of packet switching nodes and generators of traffic; it can be supplied with malefactor models in the form of traffic guns disguised under regular multimedia traffic. The present work is the further development of methods of the rectangular communication grids analysis for nodes performing the cut-through switching. The methods are intended for application in the design of computing grids, in the development of new telecommunications devices, and in intelligent defense systems. Preliminary estimations show that the cut-through technology inherits some of the negative effects, which are associated with the traditional store-and-forward delivery of packets. A series of simulations revealed conditions of blocking a grid with its regular traffic. The results are applicable in the intellectual detection of intrusions and counter-measures planning.

**Keywords:** computing grid security, cut-through switching, traffic attack defence, performance evaluation, colored Petri net, deadlock.

#### 1. Introduction

Intelligent Defense/Security Systems considerably relay on trustworthy models of networks and intrusion (malefactor). Colored Petri nets are prospective formalism for intellectual systems, because they allow simulating neural networks [2] and other facilities of knowledge representation. At the initial stage of research, models of underlying grid and intrusion of a specific (disgusted)

form are developed [5] where an overview of the related work on the grid security aspects has been presented.

Store-and-forward (SAF) buffering of packets is traditionally used in modern network devices such as switches and routers. But sometimes SAF is a significant obstruction to the quality of service (QoS) improvement. Minimum time of the packet delivery for SAF is limited by the product of the number of intermediate nodes to the packet transmission time in the channel. The cut-through transmission of packets [3] removes this limitation, because it uses only the head of packet, which contains the destination address, for the forwarding decision. Thus, the cut-through technology of packets transmission has considerable opportunities for QoS improving.

However, preliminary estimations suggest that the cut-through technology can inherit some of the negative effects, which are associated with the traditional store-and-forward forwarding of packets.

The present work is the further development of methods for analyzing of the rectangular communication grid model, which nodes perform the cut-through switching. The methods are intended for application in the design process of computing grids [4], in the development of new telecommunications devices, and in intelligent defense systems. In [5, 8] the blocking of computing grids was studied. The prospects of grid models application lay in control tools and intelligent network security. The model is developed using a colored Petri nets (CPN) and modeling system CPN Tools [1]. CPN is a graphical oriented language for design, specification, simulation and verification of systems. This language is particularly well-suited to illustrate and simulate systems in which communication and synchronization between components and resource sharing are primary concerns. Telecommunication networks and different network technologies were modeled and investigated via CPN [6, 9].

## 2. The application of cuts-through packet switching

Two main methods of packet switching dominate in modern telecommunication systems [3]: the first is with the compulsory buffering of the packet or store-and-forward (SAF), and the second is without buffering or cut-through, another popular name is "on the fly". Hybrid switches are also applied in networks; they can be automatically reversed from the cut-through mode to the SAF mode and vice versa. Switching between the modes is based on the determination of performance and the integrity of the package. Most of the modern switches support concurrently different packet rates.

The SAF technology is traditional for most networks. It provides the packet transmission to the sender only after receiving of the packet and the check the control sum (CRC). The packet is

deleted if it shorter than 64 bytes or longer than 1518 bytes or the control sum is invalid. For the SAF method, the packet delivery time increases in proportion to the size of the packet.

The switching technology "on the fly" buffers the packet head only. The cut-through switches do not produce the packets selection; therefore they are the fastest in its class. The disadvantage of this switching is that it transmits any packets including with incorrect control sum. In some cut-through switches, ICS (interim cut-through switching – intermediate switching on the fly) method is used, which filters packets with a length less than 64 bytes. The cut-through switches [3] are primarily used in data centers, where it is necessary to ensure the continuous transmission of a large traffic value with minimal delays.

#### 3. Model of grid structures with cut-through switching nodes

In telecommunication networks, one of the basic components is the active equipment such as switches or routers. Models of communication rectangular grids [4] with the basic element represented by the switch model with SAF method are studied in [5, 8]. Let us consider the construction of the node model with a direct transmission of a packet from port to port or the cutthrough switching.

The used color sets, functions, variables and value are described in [5]. For construction of grid model we use two main models: node model with cut-through switching, as a communicational device, and model of a traffic generator, as a terminal device. All models were constructed in CPN Tools.

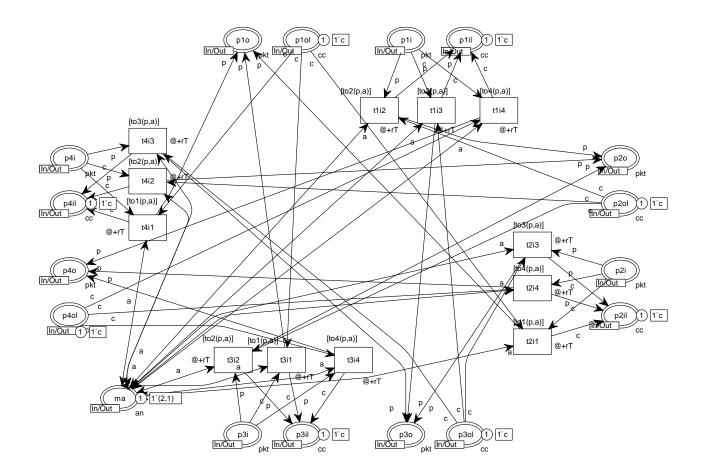

## 3.1. Node model with cut-through switching

The node model is based on the standard packing switching procedures [3] of the modern networks and grids which provide the model relevance. The model of the node with the cut-through switching is shown in Fig. 1. It is a model of network device for composition of the rectangular grid model. There are four ports in the node model which provide the full-duplex mode of work in two-directional mode for transmitting and receiving packets simultaneously. Each port consists of four places: output port buffer *po* and its capacity limit place *pol*, input port buffer *pi* and its capacity limit place *pil*. For specification of all ports, an index of port is added to the port name. The node ports' places are situated on the sides of a square for a future composition of the grid: the upper port is the first port with places *pol*, *poll*, *pil*, *pill*; the right port is the second port with places *po2*, *pol2*, *pi2*, *pil2*; the bottom port is the third port with places *pi3*, *pil3*, *po3*, *pol3*; the left port is the fourth port with places *pi4*, *pil4*, *po4*, *pol4*. According to the cut-through switching method, there is

no buffer in the model. The ports places have a color set pkt, the limit places have a color set cc, and they are contact places for the grid composition.

Fig. 1. Model of a communication node.

The system of nodes' addressing uses two integer numbers (i, j), where the first number is a number of row and the second is a number of column in the grid. Contact place na contains address of the node.

The output channel of a port is modeled by the two places: *po* and *pol*. The input channel of a port is modeled by the two places *pi*, *pil* and three transitions for each possible direction of transmission (upper, bottom, left or right). The name of transition is *ti*; for describing the redirection from the input to output port, two indexes are added. For example, transition *ti34* transmits a packet from the input port *pi3* to the output port *po4*.

Each transition has a guard function for the packet redirecting and two timed parameters rT, the receiving delay time of a packet, and chT, the transmitting delay time of a packet.

According to the cut-through switching algorithm [3], a packet is redirected from an input port to an output port if the output port is free. In the node model, special predicates are used for definition

of the destination output port [5], they are represented as the guard functions of transitions. For instance, the predicate to3(p,a) defines output port number three for a packet forwarding, were p contains the information of the packet (destination address, sender address) and a is address of a current node. Modeling of static switching and routing tables is studied in [6, 9].

In the initial marking, all the limit places of ports  $pil^*$  and  $pol^*$  contain a token l 'c which defines the port capacity; all input  $pi^*$  and output  $po^*$  places of ports are empty, there are no tokens in the corresponding places. Communication node model has a name according to the number of row and column in the grid, for example node n2-1 is a first element of second row in the grid structure.

#### 3.2. Model of traffic generator

For investigation of QoS parameters of the grid structure the model of the traffic generator was constructed. This model consists of the following parts: receiving, sending and computing [5] submodels.

The sending part describes the process of traffic generation, the intensity and type of the traffic function distribution, rules of packet sending. Each packet consists of a destination address, a sender address, a string with some content and timed stamp of the sending time.

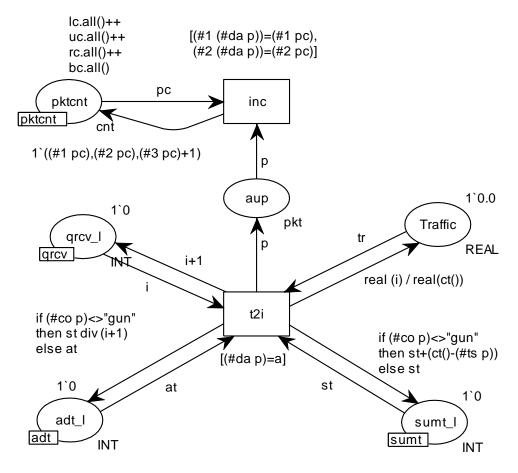

The receiving part of the model does not process an incoming packet; all packets are used in the computing part for QoS parameters calculation. The model of the computing part is shown in Fig. 2.

Fig. 2. Model of traffic generator: computing part.

Place *qrcv* contains a number of all received packets in the grid, place *pktcnt* contains a number of received packets for each terminal device, place *Traffic* describes a grid performance (packets/MTU), place *adt* is an average packet delivery time; abbreviation MTU denotes a model time unit applied for the time scalability. Terminal devices are named according to the first letter of border names, for example "right" border device has name *r*-indexes, *r*3-1 is a first right terminal device in third column of grid. Model construction for a measuring fragment (computing part of a model) was studied in [6, 7].

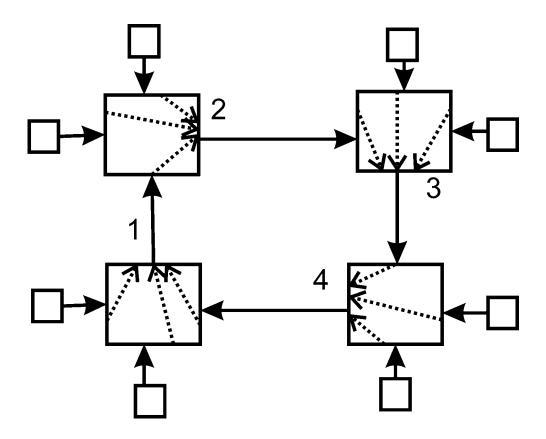

#### 3.3. Model of grid structure

Model of grid structure is a composition of a communicational device models and a terminal device models [4, 8]. Device models are submodels and according to a hierarchical structure of CPN Tools [1], all submodels are represented as transitions; in our case they are supplied with address places situated in the main page of the grid model. Model of the grid structure with the cutthrough switching is shown in Fig. 3. It is a model with current marking of the simulation process; there are three packets in the grid.

For example, the submodel of node with index (1,2) is represented on the main page as transition n1-2 and address place 12a. The submodel of bottom terminal device with index (3,2) is represented on the main page as transition b3-2 and address place 32a.

1`(0,2) 1 (0,1) 121i 1110) 111i (111il)1)1'c (121ol) 1 1 c 134i 124i 124il (1 1`{da=(1,0),sa=(i 38616}@638621 (1240) (1) 1 c 1 1`(1,0) 124ol(1) 1`c 13a (1) 1`(1,3) {da=(1,0),sa=(3,1),co="b->l",ts=6 (2110 38613\@638618 1`(2.3) 1`(2,0) 234i 23a 1 1`(2,3) 20a (1) 1`(2,0) 214il (1 234il 224il 1 1 c (2140) 224q1`{da=(3,1),sa=(3,2),ca 224ol) A 214ol(1)|1`c 234ol(1) 1`c 321i 321ii 31111 1 1 6 3210 311i (321ol) 1 (3,2) 1 (3,1) 1`(3,1) b3-1

Fig. 3. Model of grid structure of size 2x2

Places with index (\*) and suffix \*o, \*ol, \*il, \*il are contact places, which describe output and input ports of the grid nodes and terminal devices. According to the composition rules [6, 8], all ports of communication devices have two description forms on the main page with respect to the enumeration in each of two connected nodes. The first and fourth ports of each node are represented with an index of this node; the second and third ports are union with the first and fourth ports of next nodes and have indexes of next nodes. For example, the place 221i is the first input port of node n2-2 and the third output port of node n1-2. The bottom row and right column contact places describe the first and fourth ports of nodes, which do not exist in the model. These places are used for connecting of bottom and right terminal devices. For example, the place 2340i is the fourth output port of node n2-3, but there is no node with indexes (2,3) in the grid. This place is merged

with the input port of terminal device r3-2. In the model, there are no contact places with indexes of border devices.

#### 4. Simulation of Grid Workload

For QoS parameters estimation, simulation of the grid workload was implemented. The grid workload is obtained using the traffic generations, described in the previous section, attached to the grid border. Intensity of the workload and timed delay rT of sending packets are basic parameters of the model, whose influence on the grid behavior was estimated. For Poisson distribution with different intensity, a grid performance and an average packet delivery time were studied. The obtained results were compared with characteristics of the grid model having SAF forwarding. Buffer size in this model is supposed equal 10 packets.

Table 1 shows the result of the grid investigation via regular workload for SAF and cut-through switching modes.

| Workload       |                   | Average packet      | Grid performance |

|----------------|-------------------|---------------------|------------------|

| intensity (wl) | Type of switching | delivery time (MTU) | gp (packets/MTU) |

| 50.0           | cut-through*      | 10                  | 0,14             |

| 50.0           | SAF               | 21                  | 0,14             |

| 30.0           | cut-through*      | 11                  | 0,23             |

| 30.0           | SAF               | 21                  | 0,23             |

| 16.0           | cut-through*      | 11                  | 0,44             |

| 16.0           | SAF*              | 22                  | 0,42             |

Table 1. Grid characteristics under workload

Step=1000000, rT=5, bs=10, k1=2, k2=2; \* – the grid comes to a full deadlock – no permitted transitions.

Workloads with 50.0 and 30.0 intensities are light workloads for investigated grids. The grid performance is equal for two switching modes; the average packet delivery time for SAF mode is twice greater than for cut-through mode. Workloads with intensity about 16.0 are middle workloads for the investigated grids. The grid performance of cut-through mode is greater than for SAF mode, the average packet delivery time for SAF mode is twice greater than for cut-through mode. For big size grids, the average packet delivery time for SAF mode will be a few times greater than for cut-through mode.

Cut-through mode switching works faster than SAF mode, but it has the important disadvantage: network with cut-through mode switching is blocked if destination ports are busy. Ports are cleared after executing a special system time procedure (TTL). Some incoming and outgoing packets are lost. Ports clearing function is not simulated in this paper.

An example of a full deadlock is shown in Fig. 4, where inscriptions on the arcs indicate the number of blocked ports in nodes.

Fig. 4. An example of a full deadlock.

There are four packets in each node: one packet is in the output port, three packets are in the input ports and the destination ports of these packets are the same. The current node can not transmit the packet from output port to the next node, because the next node cannot redirect the incoming packet, because the destination port of this packet is busy. As a result of this clinch is the full deadlock of grid. Thorough explanations could be illustrated by a sequence of pictures from the first mutual blocking of a few nodes via extending the blocked areas to the complete deadlock shown in Fig. 4.

Grid behavior under traffic attacks and workload was studied for grid structures with store-and-forward mode [5, 8].

#### 5. Conclusions

Models of grid structures with cut-through switching nodes were constructed in the colored Petri net form. Security of grid structures, in particular possibility of deadlocks, was investigated under workload in the environment of modeling system CPN Tools. The importance of obtained results for the grid computing domain consists in the conclusion that modern architecture of the switching devices does not guarantee the grid security. Special protocols which involve interoperability of a several nodes should be developed for the deadlocks detection and avoidance.

A future research direction will be to investigate the grid structures with cut-through switching nodes under a workload and traffic attacks; to study types of deadlocks and QoS characteristics of grid under disguised traffic attacks; to construct a re-enterable model [9] for investigation of grid structures with a big size, where initial characteristics of grid are model parameters.

The models are applicable in the intelligent defense and security systems of computing grids.

#### References

- Jensen, K., Kristensen, L.M. Coloured Petri Nets: Modelling and Validation of Concurrent Systems. Springer, 2009, 384 p.

- 2. Koriem Samir M. CN-Nets for Modeling and Analyzing Neural Networks. J. King Saud Univ., Vol. 13, 2001, Comp. & Info. Sci., pp. 19-47.

- 3. Liberzon Daniel. Switching in Systems and Control. Published by Birkhäuser Boston, 2003, 230 p.

- 4. Preve, N.P. (Ed.). Grid Computing: Towards a Global Interconnected Infrastructure. Springer, 2011, 312 p.

- 5. Retschitzegger W., B. Pröll, D. A. Zaitsev, T. R. Shmeleva. Security of grid structures under disguised traffic attacks. Cluster Computing, 19(3) 2016, pp. 1183–1200.

- Sakun A.L., Zaitsev D.A. An Evaluation of MPLS Efficacy using Colored Petri Net Models. Proceedings of International Middle Eastern Multiconference on Simulation and Modelling (MESM'2008), Amman (Jordan), August 26-28, 2008, pp. 31-36.

- 7. Shmeleva T.R., Zaitsev D.A. Switched Ethernet Response Time Evaluation via Colored Petri Net Model. Proceedings of International Middle Eastern Multiconference on Simulation and Modelling, August 28-30, 2006, Alexandria (Egypt), pp. 68-77.

- 8. Zaitsev D.A., Shmeleva T.R., Retschitzegger W. and Proll B. Blocking Communication Grid via Ill-Intentioned Traffic. 14th Middle Eastern Simulation & Modelling Multiconference, February 3-5, 2014, Muscat, Oman, pp. 63-71.

- 9. Zaitsev D.A., Shmeleva T.R. Parametric Petri Net Model for Ethernet Performance and Qos Evaluation. Proceedings of 16th Workshop on Algorithms and Tools for Petri Nets, September 25-26, 2009, University of Karlsruhe, Germany, pp. 15-28.

UDC 004.05

## Design and implementation a software for water purification with using automata approach and specification based analysis

Sergey Staroletov (Polzunov Altai State Technical University)

The paper covers design and developing software for hardware plant for water purification, the architecture for it, received automaton diagrams of water preparing and normalization based on customer specifications and requirements. Discussing the components of the system, layers of abstractions, verification points, issues to build it. The way of developing well-qualified suchlike systems based on specifications is given.

Keywords: Water purification, software, automaton, energy conservation, verification, requirements engineering

#### 1. Purpose and novelty of the project

Our university received an order for the research work to design and development software under the UN grant for developing countries in the field of energy conservation.

A customer is developing the hardware stand providing preparation of distilled water of the given temperature and testing the energy consumption and water consumption of various connected devices (for example, washing machines and dishwashers).

Water purification is necessary for this project because existing standards [1] for measuring energy consumption and water consumption presuppose to work with distilled water (water preparation process) at a given temperature (water normalization process).

It was necessary to design and implement software that automatically control preparing large volumes of purified water, also measures the energy and water consumption of the connected devices and generates some reports.

The novelty of the project is following: all water preparation and equipment testing should be performed without user intervention by the automatic operations in the hardware stand and the operator's job is only to select the mode, to set parameters and then run the process.

From the programmatic point of view, novelty consists primarily in mandatory to implement algorithms for water purification and control of hardware devices to it, these algorithms must be primarily reliable because water is supplied under high pressure, is heated using amperage of tens of amperes, and all possible exceptional operations must be processed.

These algorithms must include various multithreaded interactions because the states of the devices are not correlating to each other, and it is necessary to examine at any time the devices, update the interface, make decisions about the further operational logic.

Therefore, it was necessary to design the software architecture properly and verify the proposed algorithms before using them.

This paper covers the software architecture design and algorithms developed by the author, also verification and testing, main issues and the questions about formulation the requirements for building these systems.

The results partially were obtained within the RFBR grant (project No. 17-07-01600).

#### 2. A bit about the hardware

In this article, there is no purpose to describe the hardware. The author did not design and develop it but implemented software for the available hardware. Here will be given information about the components to get an idea of the operation of the equipment as a whole.

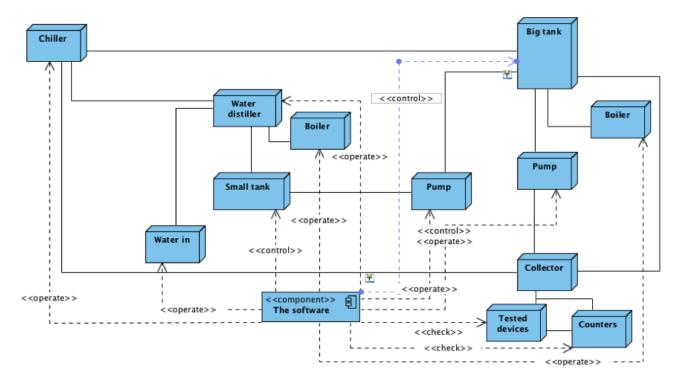

Here is a water purification hardware stand (Figure 1):

Fig. 1. Diagram of hardware components using in the stand

1. A chiller (conditional element) for cooling the water. Chiller is operated by a special software to set the output temperature based on current air temperature and desired temperature.

- 2. An aqua-distiller (with heating element) to create a distillate from given water.

- 3. A small tank for obtaining the current distillate with a level sensor.

- 4. Large storage tank for obtaining final water with level sensors and a heating element for heating.

- 5. A small pump for pumping water from a small tank into a large storage tank.

- 6. Main pump for water circulation in the whole system (a variable frequency drive).

- 7. Digital equipment for measuring water consumption (water flow meters) and electricity meters.

- 8. Digital devices with digital and analog I/O ports to connect devices, start relays and sensors to serial port adapters.

- 9. A collector, through which the devices checked for energy saving are connected and through which the prepared water circulates from the tank.

- 10. Various valves for switching water flows between the aqua-distiller, the storage tank, the collector.

The interaction with the hardware is implemented on the basis of the Modbus [2] protocol by using digital multi I/O devices, on/off switching relays, obtaining status data via analog and digital inputs. Linear interpolation algorithms are used to translate analog sensor values into the digital form.

The special software component called Devices Map has been implemented to link the devices from devices list (Figure 1) into concrete I/O ports on concrete digital I/O modular devices connected to concrete serial ports on the computer.

## 3. System architecture

The designed application inside consists of:

- A device(hardware) layer a single software interface for the devices is created and implementation classes for each device in the system are created. This layer is built on the top of the Modbus protocol (and GOST IEC protocol [3] for the electric meters) and own actions for every device (to read some values from device's registers).

- Serial port layer. Every device is known by its port (Device Map tool causes a hash table device port) and for the correct work, it must reserve the port because at any time only one device can operate on the port. Each port layer abstraction should work in **Device Getter Thread**, and to acquire the port to transmit data we must wait for

any other device freeing the port. It could be implemented as a synchronization primitive (mutex with lock/unlock).

- A layer of objects. Every device state is represented as an object. If we want to acquire a device state we can get the state in every moment by accessing a getter method in a corresponding object which stores the last received state from a device. Object stores current data and periodically **Device Getter Thread** updates it.

- Updater Thread is a foreground process that periodically asks all the objects and gets their state, then updates corresponding UI elements.

- UI is a mnemonic representation of the system; it has background images and dynamic elements (text values of system parameters such as temperature, pressure, on/off boxes to show states, graphic objects to draw some primitives like level meter, animations to show chiller's fans) which are updated by Updater Thread. UI also can work in manual operator's mode when operator press to the devices on the mnemonic diagram to start and stop them.

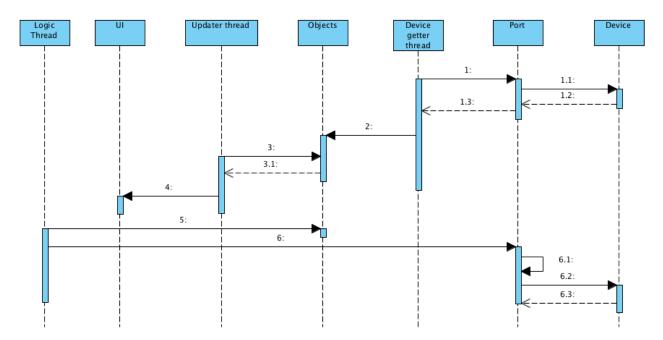

An example of components inter-operation sequence is shown on Figure 2.

Fig. 2. Sequence diagram of possible components inter-operation

Here, **Device Getter Thread** starts to update the device's state. It requests a **Port** for given device, possible wait for the port, then when the port is free it runs device state update routine (which constructs Modbus or different protocol message corresponding to the device number and device updating algorithm), then gets the state and updates the **Object** to its

device. Then **Updater Thread** gets the current state of the device object and updates the **UI** corresponding to the new device state value.

Described in the next sections **Logic Thread** can get the object state and make decisions based on it. During the logic cycle, it can turn on/off a special device (for example, starts/stops the main pump). It asks port when it becomes free for the corresponding device, then acquires it and executes a routine in the **Device layer**.

Implementing these ideas is not very difficult to a developer who knows how to operate with the threads and how to lock resources from data races with using simple locking. Implementing the device layer requires reading its specifications, understanding the protocols by using original software and looking to transmitting and receiving data. The correctness of it is checking by testing techniques.

#### 4. Requirements for development

Requirements engineering [4] is a way to collect customer's requirements for the system. Our goal now to help software engineers work together with the customers to build adequate error free software because the definition of the word "error" is nonconformity of program's behaviour to the original specification of requirements. Why not use this project to analyse such documents like "Requirements for development" to extract the correct specifications from it and integrate the requirements engineering, developing and verification processes to minimize troubles of producing such systems?

About the water purifying software. The software engineer can create the software to start/stop the devices and watch the states based on devices specifications but cannot create the whole inter-operation system because he usually doesn't know anything about purifying the water of even what is the chiller or aqua-distiller, he needs a customer and his needs. In this project, firstly, the task of implementation of given system architecture has been done, so that the operator could run the whole process of water purifying manually by pressing keys in the application and visually monitor the result on the screen and a real installation. Further, as a result of negotiations, the algorithm of automatic actions of the program was approved in the form of the following document (some excerpts are given in Appendix A).

Here we see the description of the algorithm in some high-level form. The algorithm is based on the management of devices that were specified in the picture of the interface (like in Figure 1), and the functional is predetermined by water purifying specialist.

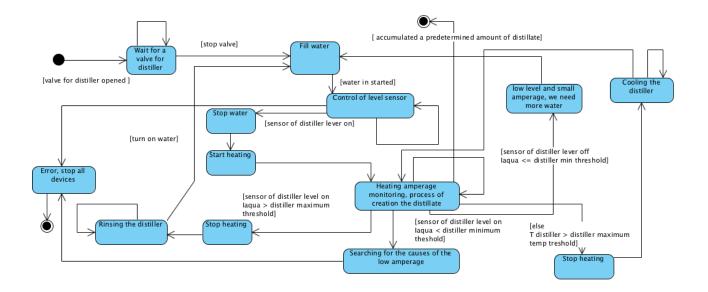

Fig. 3. State machine for water preparation